随着智能可穿戴设备、增强现实(AR)和虚拟现实(VR)等新兴领域的快速发展,对高端显示技术的需求愈发迫切。Micro/nano-LED作为先进的显示技术,以其高亮度、高对比度和低能耗等特点备受关注。具体而言,Micro/nano-LED技术中微米级的尺寸和独立像素单元的特性,可以为AR和VR等领域提供更高的像素密度和卓越的显示质量,为用户带来更加惊艳和精彩的视觉体验。然而,随着这些设备尺寸的减小,侧壁效应变得显著,影响了Micro-LED的整体性能。此外,相邻像素之间的光学串扰以及量子点对湿气的敏感性在这种微小尺寸下变得明显。为了解决上述问题,薄膜封装技术是非常有效的方法之一,但目前,对于传统的化学气相沉积(CVD)和物理气相沉积(PVD)来说,想要在如此微小的尺度上实现均匀致密,厚度可控的沉积仍存在挑战。

原子层沉积(Atomic Layer Deposition,ALD)是一种理想的纳米级薄膜气相沉积制造技术,ALD最大的特点是原子级的自限制反应,能够实现薄膜厚度单原子层级别(~1Å)的精确控制,并具有高均匀性和致密性的特点,可以显著提高器件在小尺寸下的稳定性。然而,薄膜中存在残余应力会导致薄膜的开裂和分层,严重限制先进应用中器件的性能。在以往研究中,通过工艺优化,可以有效降低单层薄膜残余应力,并实现近零应力薄膜的制备,但不可避免地会在其他性能方面做出妥协,例如阻隔性能、光学性能和机械性能,这些性能对于封装显示光电器件是至关重要的。因此,如何通过ALD工艺实现近零应力薄膜的制备,同时保持其他性能不受损,是一个重要的挑战。

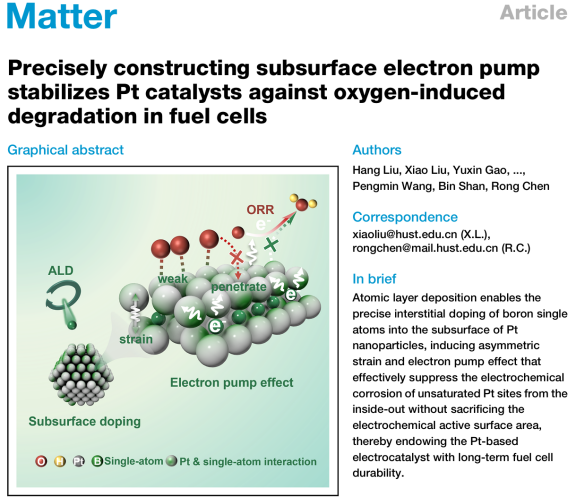

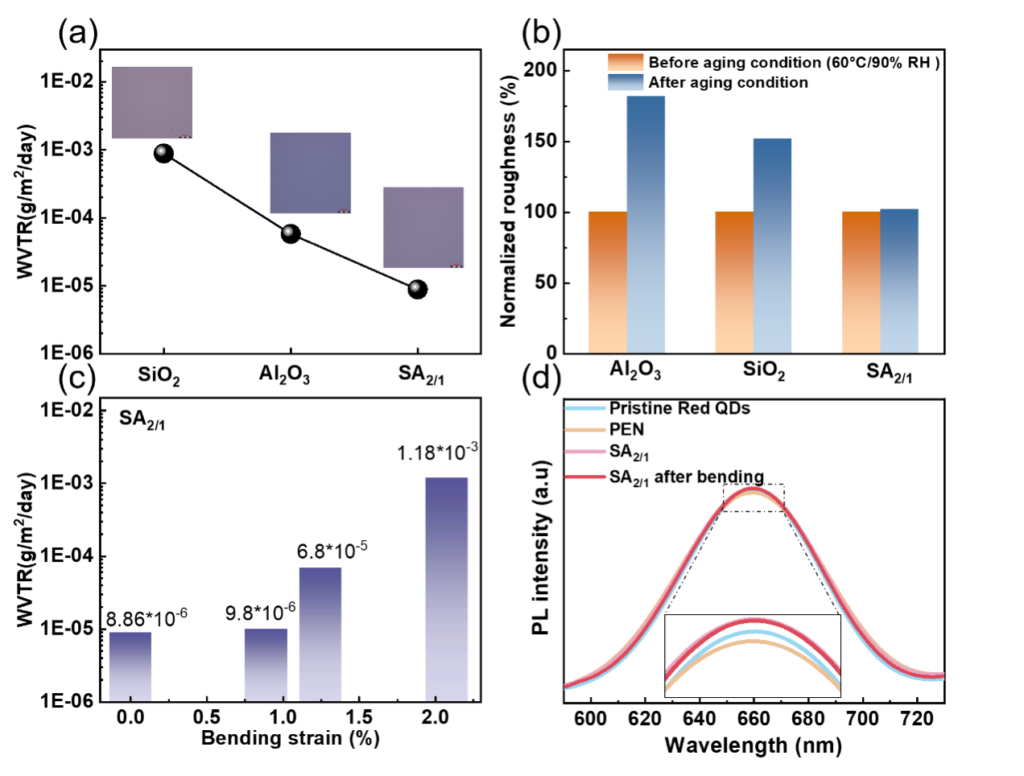

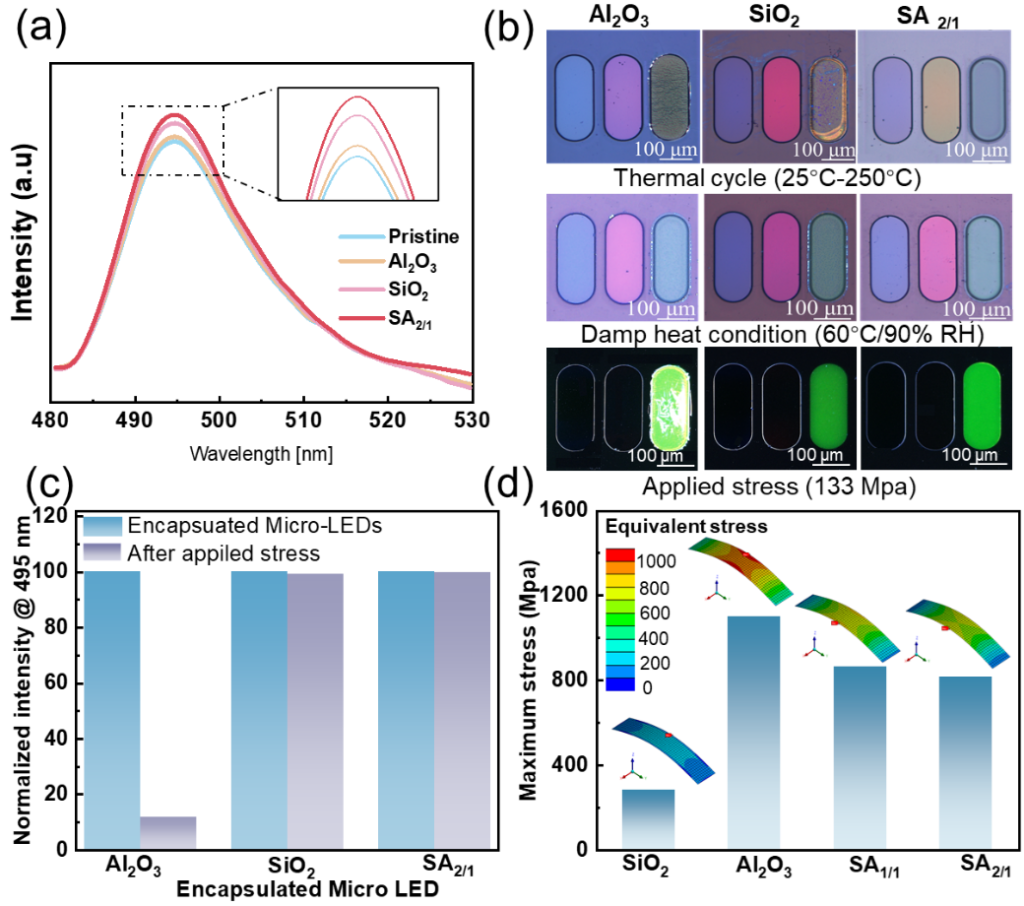

华中科技大学陈蓉教授课题组针对上述挑战,提出了反向应力匹配的ALD无机叠层复合膜设计方法,利用等离子体ALD SiO2薄膜(压应力)和热ALD Al2O3薄膜(拉应力)的不同应力特性,发展热-等离子体共温下ALD嵌套循环工艺。提出的同温沉积有效减少界面热应力,通过精确控制两种薄膜的原子级层厚与组合顺序,实现残余应力均小于5 MPa的近零应力纳米叠层封装阻隔膜制备。此外,提出的高低折射率、曲折的渗透路径以及超薄厚度的结构设计,显著提高了纳米叠层薄膜的光学透光率,阻隔性能(8.68×10-6 g/m2/day)和柔性(承受1.25%的弯曲应变)。最终应用于micro LED封装,成功提高了Micro/nano-LED在热循环、极端湿热以及外加应力条件下的稳定性和可靠性。这一成果不仅对Micro/nano-LED技术的发展具有重要意义,也为高端显示技术在各种应用场景中的推广奠定了基础。

相关文章以《基于原子尺度应力调控的纳米层状结构用于micro-LED封装》(Atomic-Scale Stress Modulation of Nanolaminate for Micro-LED Encapsulation)为题发表在期刊Nanoscale上,华中科技大学机械学院博士研究生文迪和硕士研究生胡嘉成为文章共同作者,陈蓉教授与曹坤副教授为共同通讯作者。感谢国家自然科学基金重点项目(51835005) “面向柔性量子点显示稳定化的原子层沉积跨尺度制造方法研究”对本研究工作的资助。

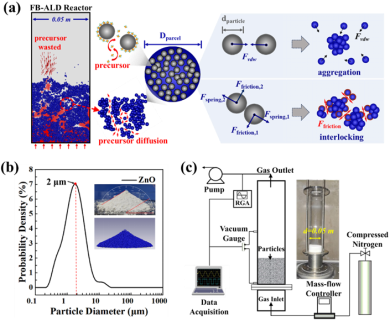

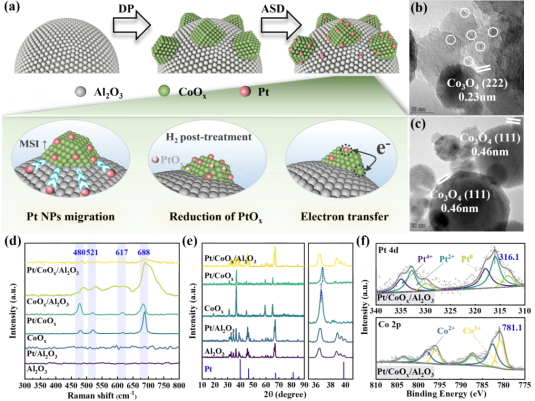

图 1 通过原子级应力匹配策略实现了近零应力纳米叠层薄膜的制备

图2 近零应力纳米叠层薄膜具有高阻隔性能(8.68×10-6 g/m2/day),柔性(承受1.25%的弯曲应变)和高透光性能

图3 纳米叠层封装的Micro LED在热循环、极端湿热以及外加应力条件下的高稳定性和可靠性。

文献链接:https://pubs.rsc.org/en/content/articlelanding/2024/nr/d3nr06169h/unauth